【STM32学习笔记】SPI协议

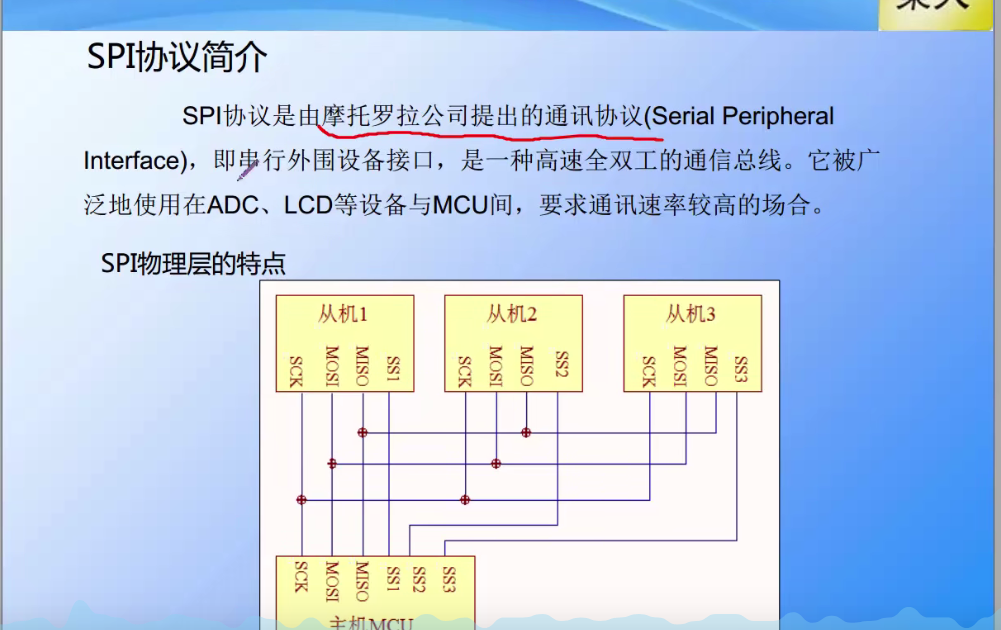

1.SPI 协议简介

1.SPI硬件层

引脚(SS,MOSI,MISO,SCK)

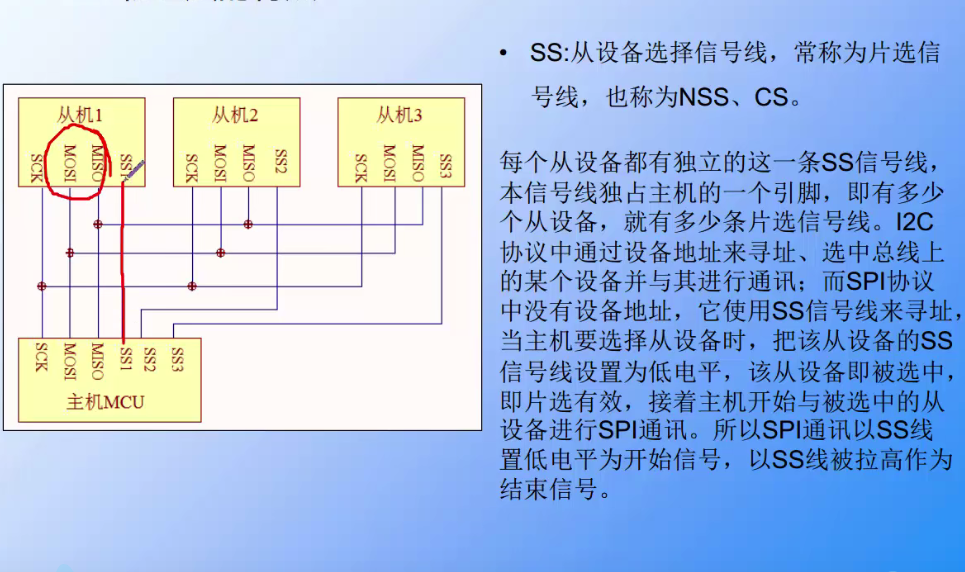

SS

从设备选择信号线,常称为片选信号线,也称CS,NSS

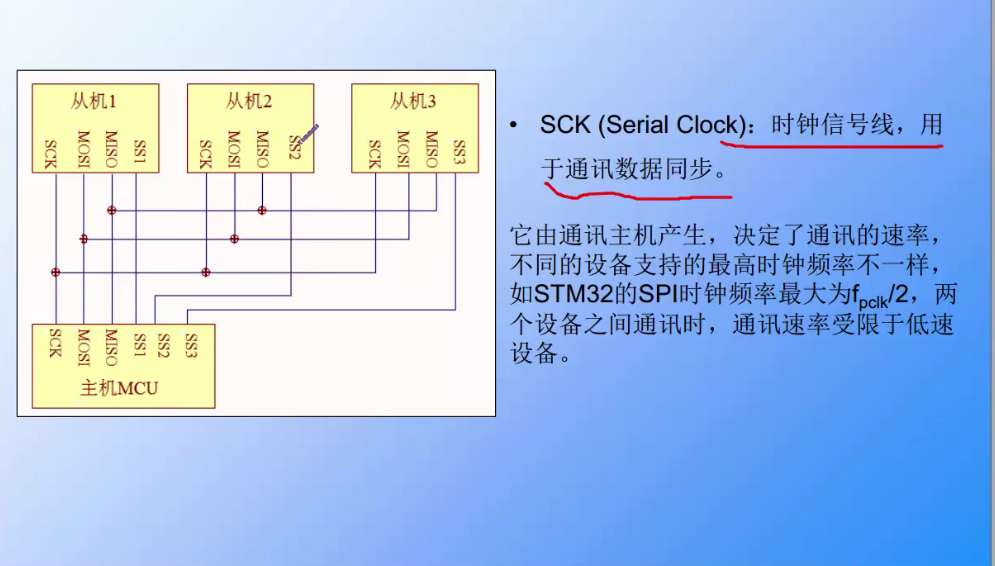

SCK

时钟信号线,用于通讯数据同步

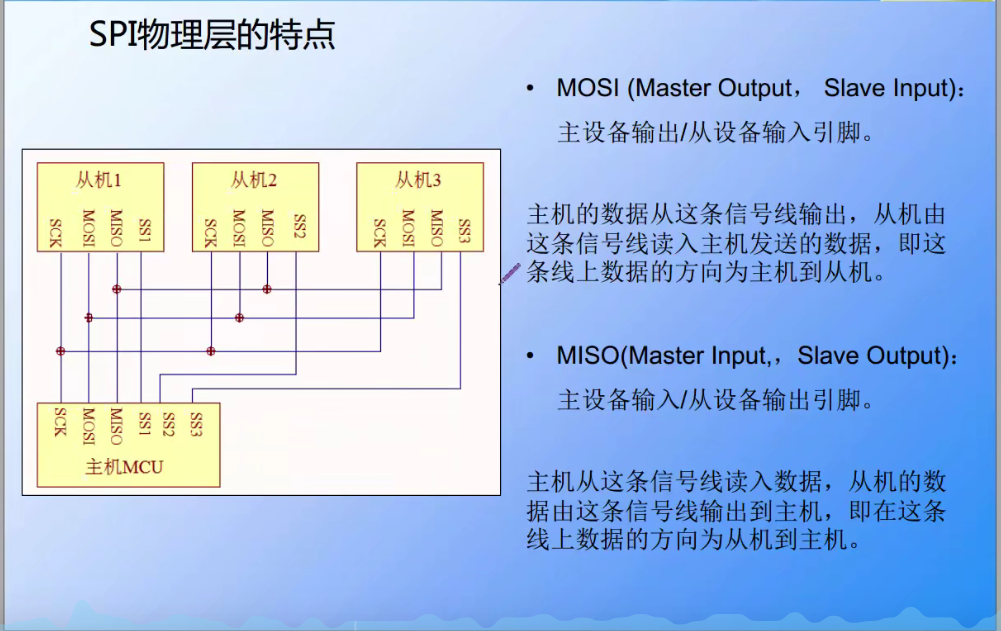

MOSI MISO

MOSI

主设备输出/从设备输入

MISO

主设备输入/从设备输出

1.SPI协议层

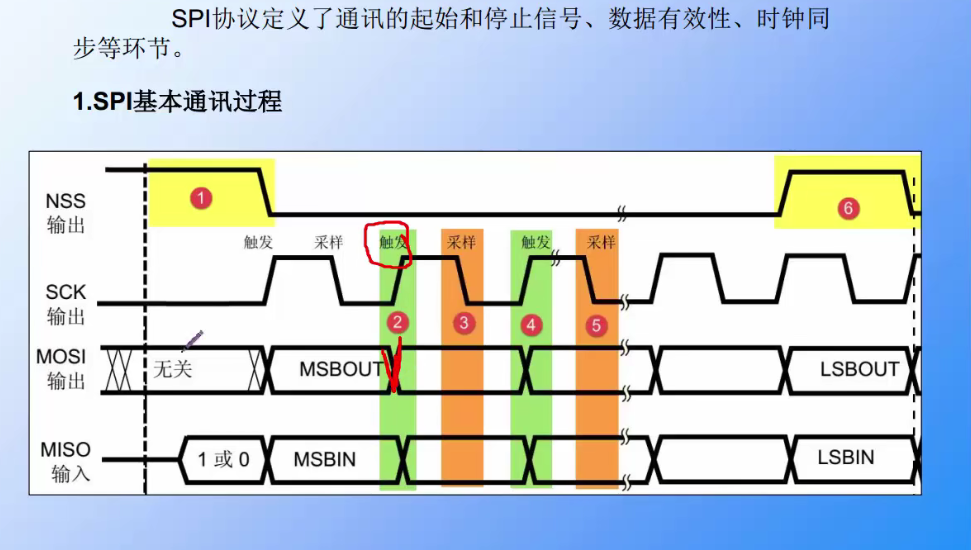

1.SPI基本通讯过程

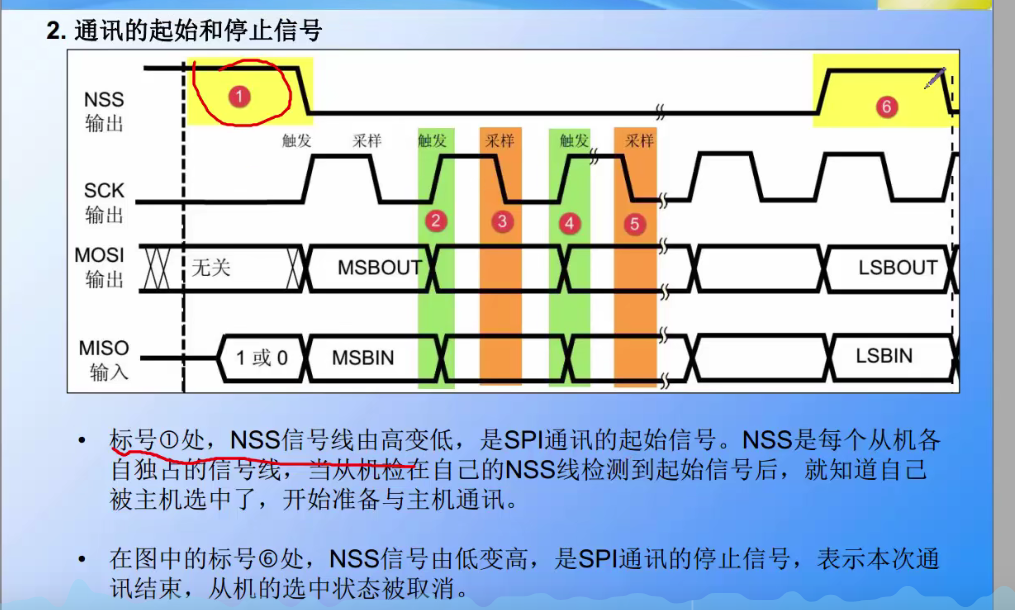

2.通讯的起始和停止信号

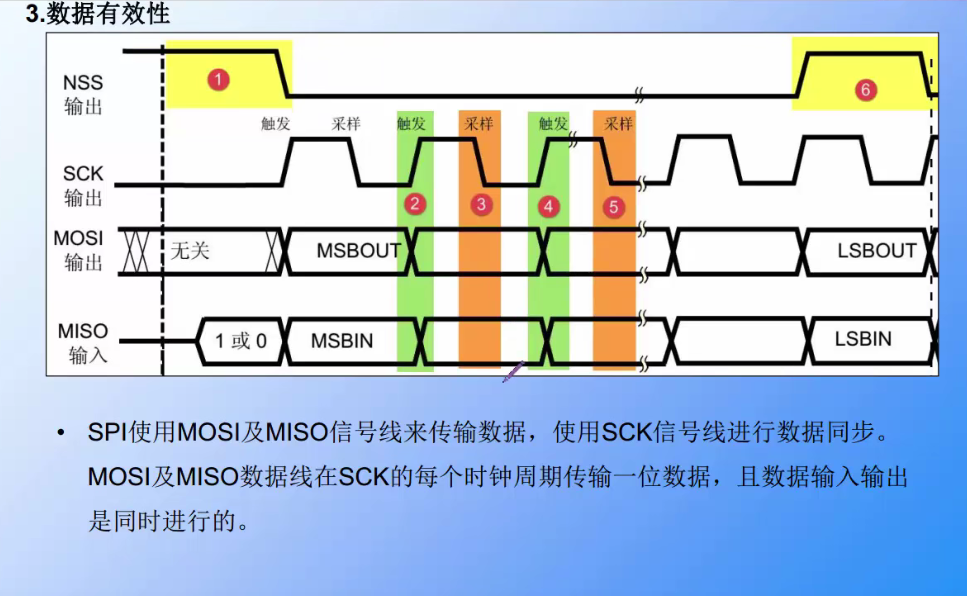

3.数据的有效性

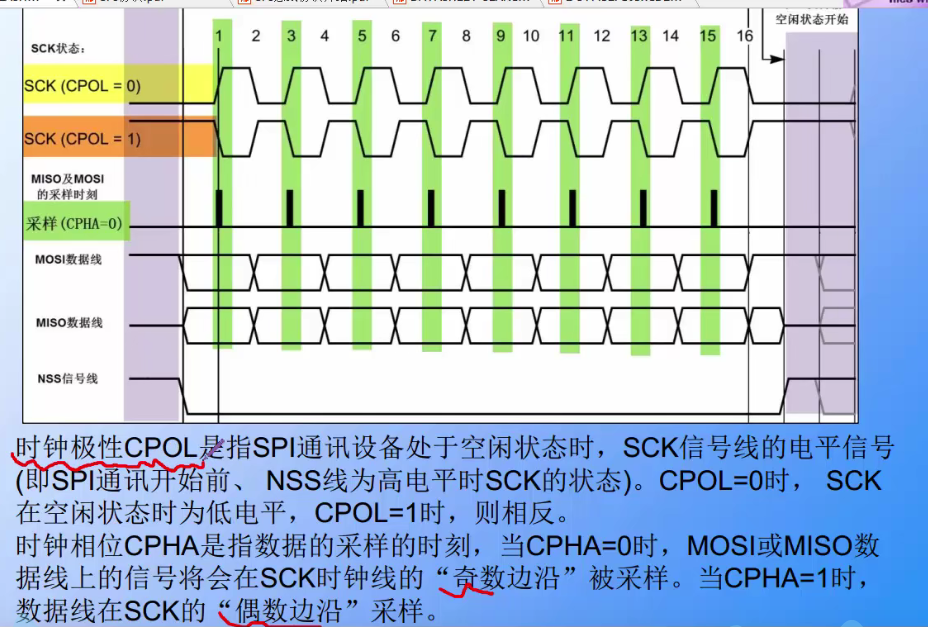

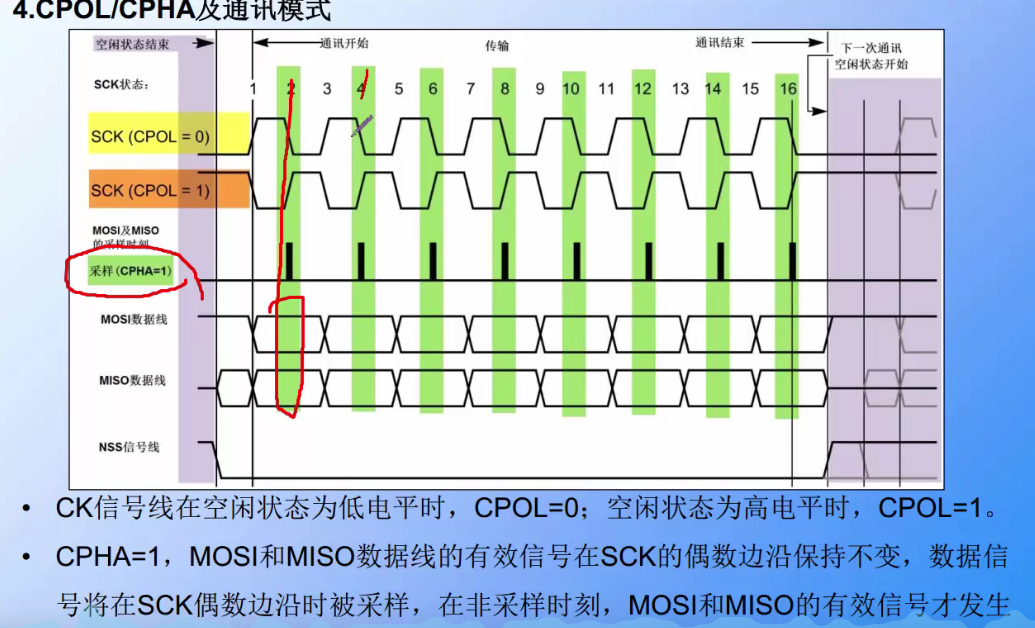

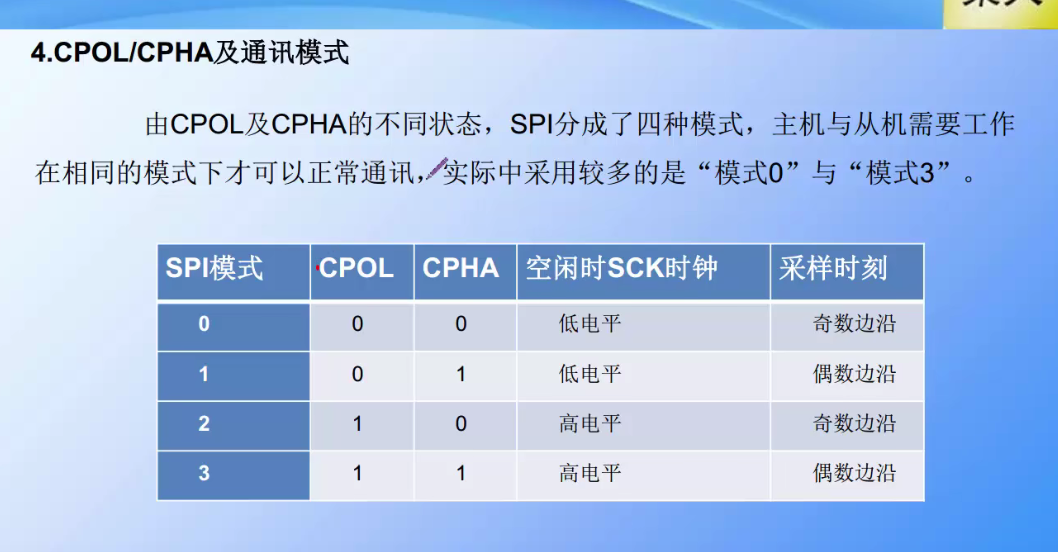

4.CPOL/CPHA及通讯模式

CPHA = 0 CPOL = 0/1

CPHA = 1 CPOL = 0/1

总结

1.CPOL控制高电平还是低电平为空闲状态

2.CPLA控制奇数边沿还是偶数边沿为采样

3.总共有4种模式

2.STM32 SPI特性及架构

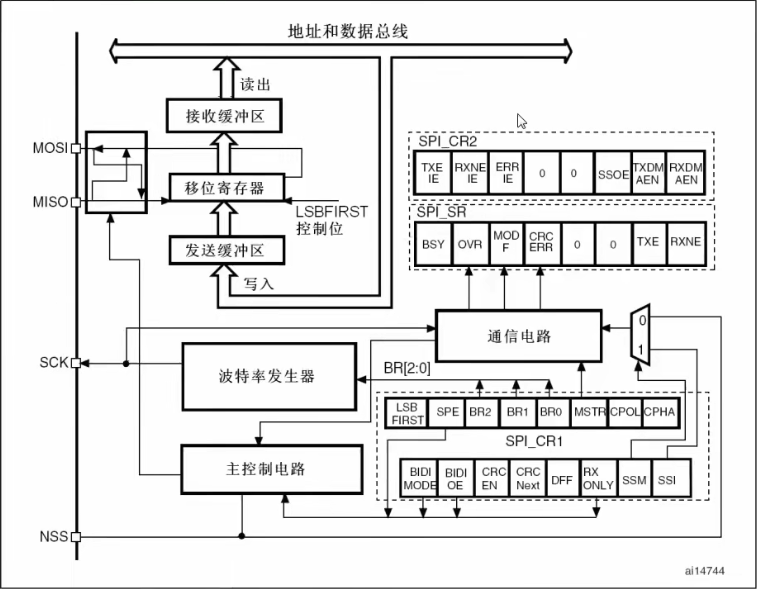

STM32 SPI架构

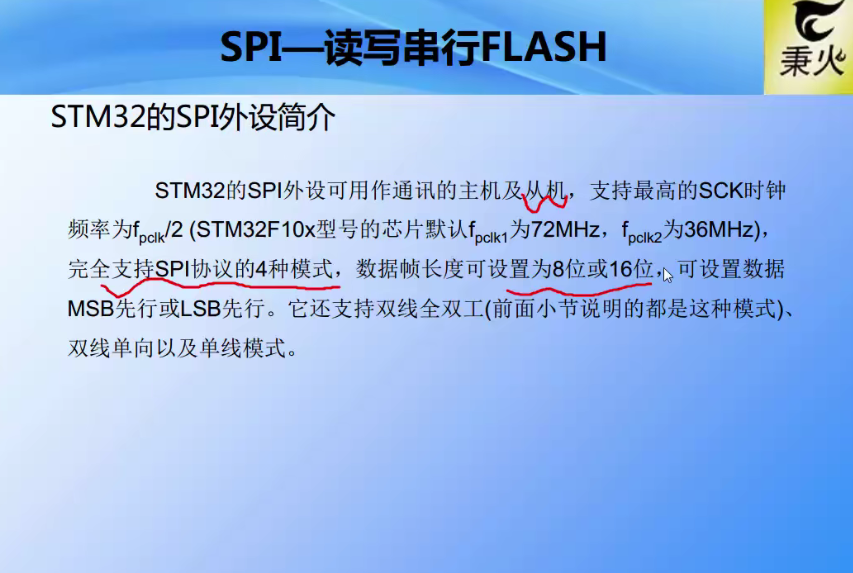

STM32 SPI简介

SPI1挂载在APB2总线上,最高36MHz。(F3)

SPI2/SPI3挂载在APB1总线上,最高18MHz。(F3)

数据帧可设置为8或16位。可设置低位或高位先行。

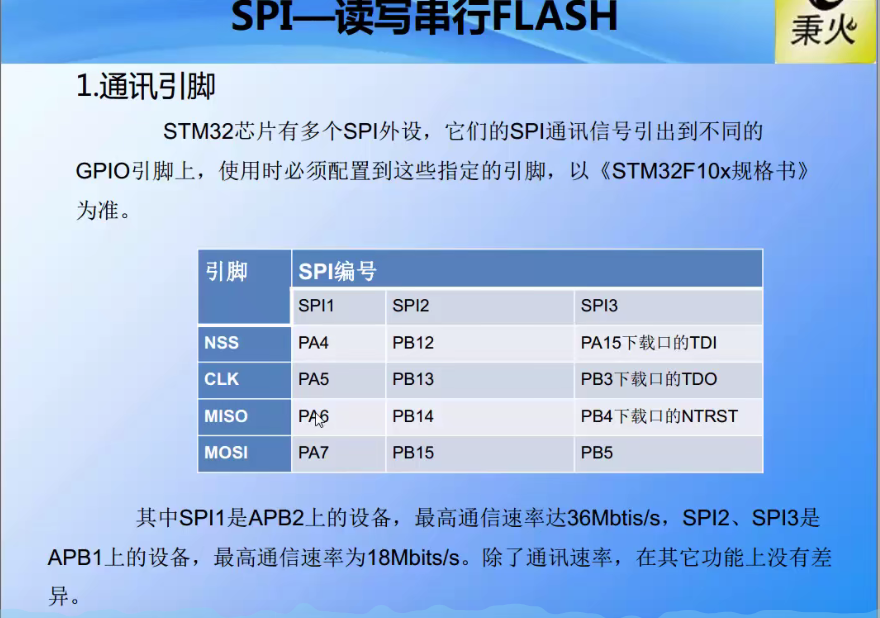

通讯引脚

SPI1

NSS PA4

CLK PA5

MISO PA6

MOSI PA7

SPI2

NSS PB12

CLK PB13

MISO PB14

MOSI PB15

SPI3

NSS PA15

CLK PB3

MISO PB4

MOSI PB5

时钟控制逻辑

控制部分

CR1 的 BR[0:2]

APB1的fpclk = 36MHz APB2的fpclk = 72MHz

作为主机的时候用来分频

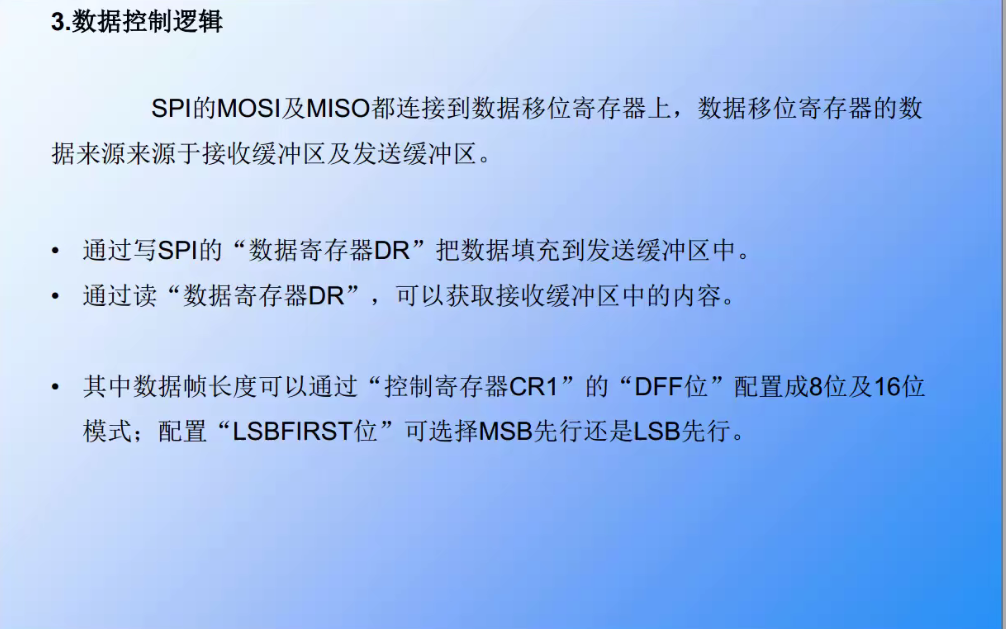

数据控制逻辑

移位寄存器是有两个,一个用来发送,一个用来接收。

当写入数据寄存器DR,数据会被填充到发送缓冲区。

当读数据寄存器DR,可以获取接受缓冲区的内容。

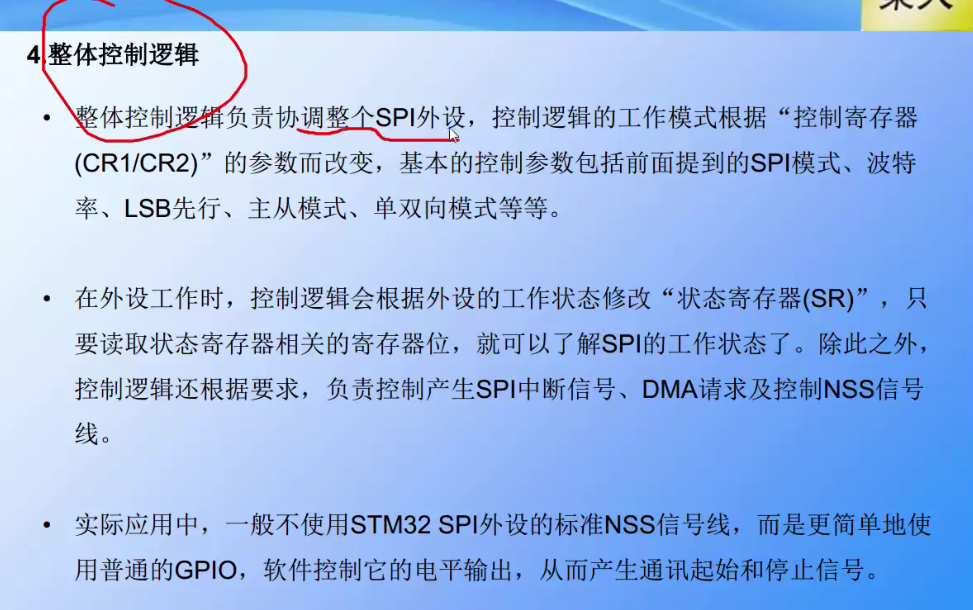

整体控制逻辑

控制寄存器

CR1/CR2

可以控制SPI模式、波特率、LSB先行、主从模式、单双向模式,中断请求等。

状态寄存器

SR

记录当前SPI的工作状态。

NSS引脚

这个可以由软件选择特定的GPIO引脚初始化为推挽输出替代SPI固定的NSS引脚

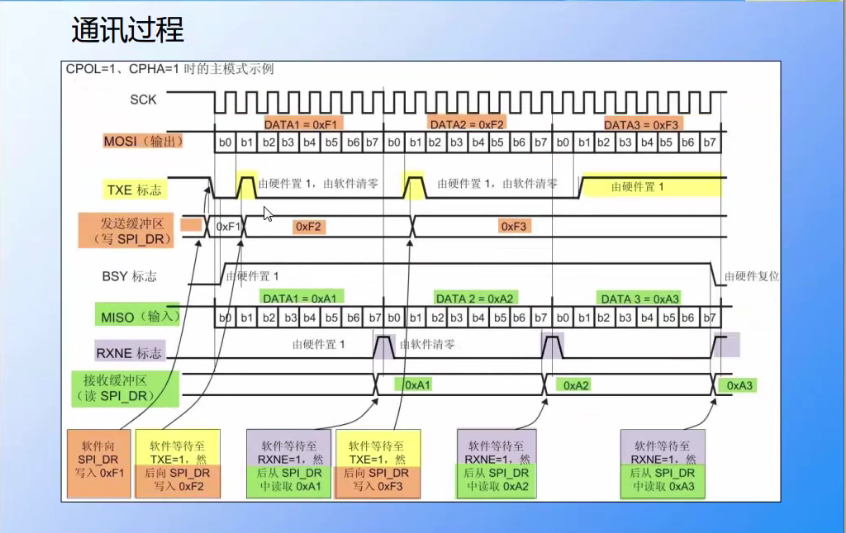

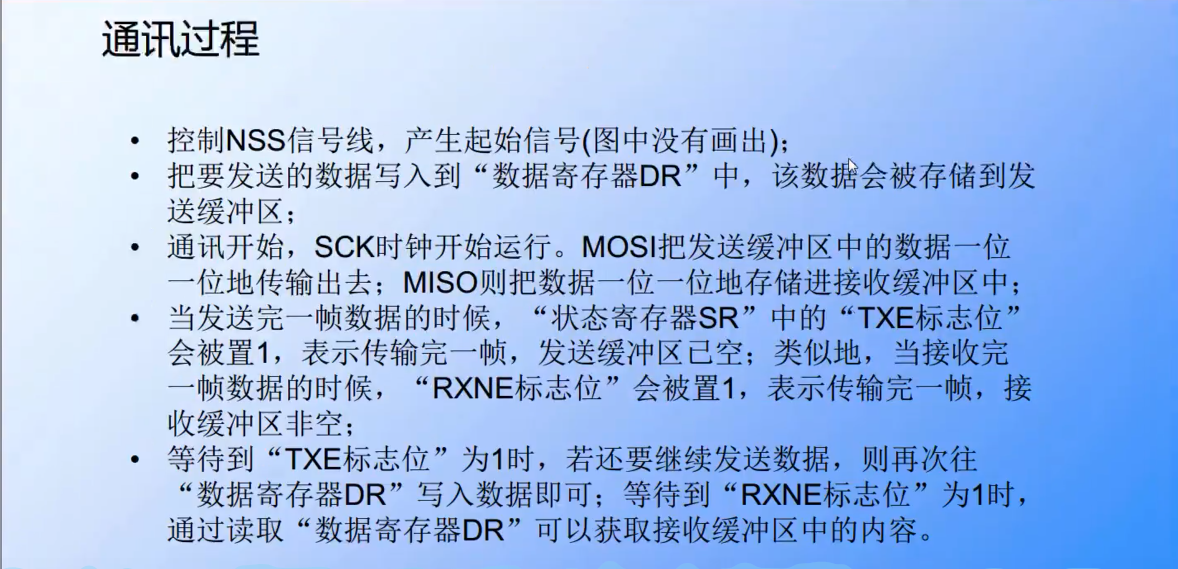

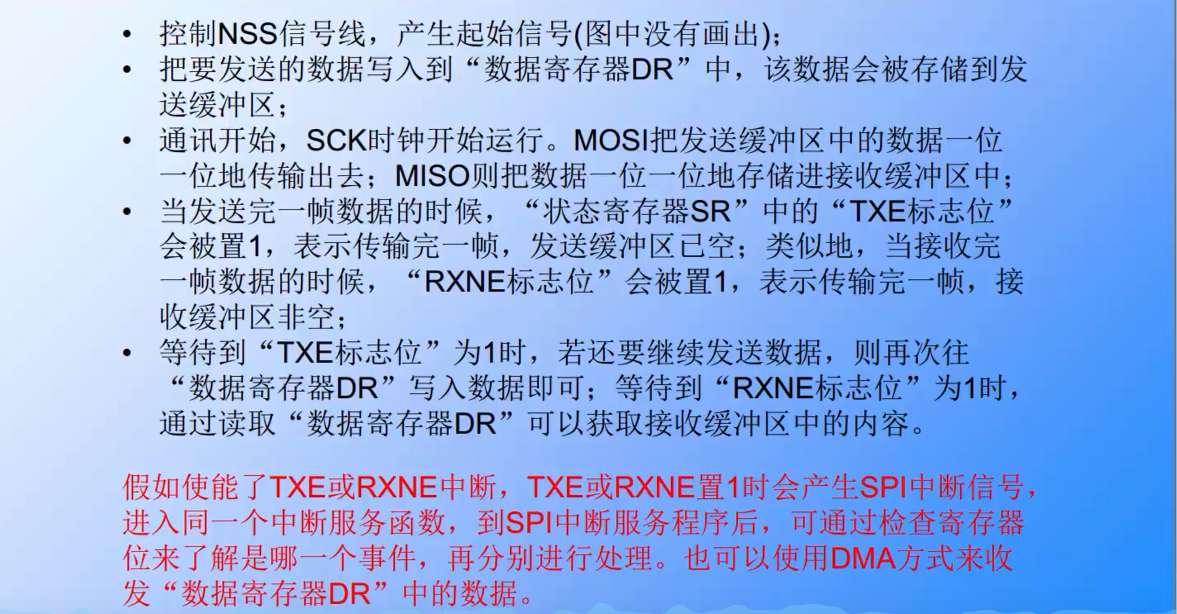

通讯过程

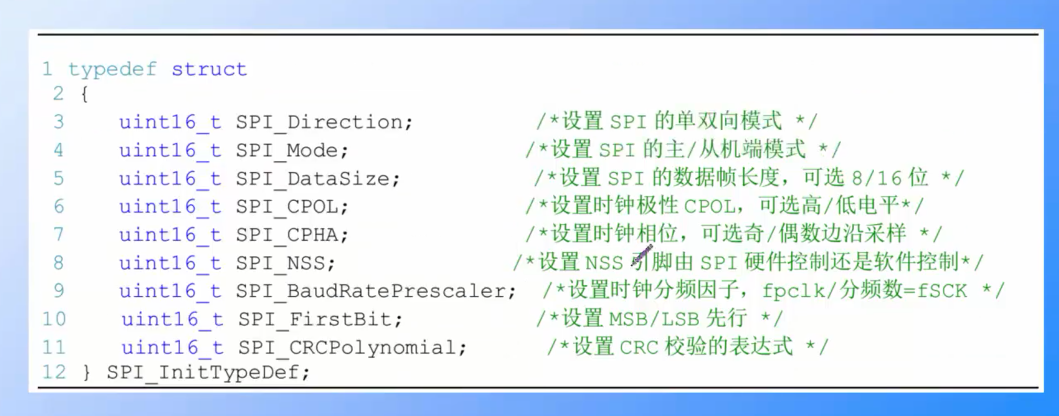

3.STM32 SPI初始化结构体

1.SPI_Direction

2.SPI_Mode

3.SPI_DataSize

4.SPI_CPOL & SPI_CPHA

5.SPI_NSS

6.SPI_BaudRatePrescaler

7.SPI_FirstBit

8.SPI_CRCPolynomial

本博客所有文章除特别声明外,均采用 CC BY-SA 4.0 协议 ,转载请注明出处!